DE LA RECHERCHE À L'INDUSTRIE

CEZ

# leti

**Annual Research Report 2014**

**Leti** is an institute of **CEA**, a French research-and-technology organization with activities in energy, IT, healthcare, defence and security.

By creating innovation and transferring it to industry, Leti is the bridge between basic research and production of micro- and nanotechnologies that improve the lives of people around the world.

Backed by its portfolio of 2,200 patents, Leti partners with large industrials, SMEs and startups to tailor advanced solutions that strengthen their competitive positions. It has launched more than 50 startups. Its 8,000m² of new-generation cleanroom space feature 200mm and 300mm wafer processing of micro and nano solutions for applications ranging from space to smart devices. Leti's staff of more than 1,700 includes 200 assignees from partner companies. Leti is based in Grenoble, France, and has offices in Silicon Valley, Calif., and Tokyo.

Visit <a href="http://www.leti.fr/en">http://www.leti.fr/en</a> for more information

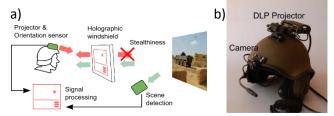

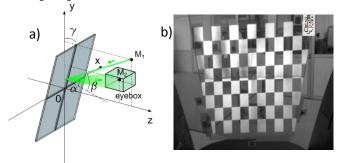

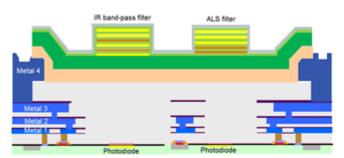

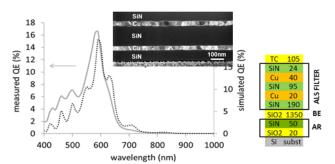

Within CEA-Leti, **Optics and Photonics** activities are focused principally on big industrial markets of photonics: various wavelengths imaging (visible, infrared, THz), information displays, solid state lighting, optical data communications, optical environmental sensors. The R&D projects are performed with industrial and academic partners. The industrial partners of the Optics and Photonics department range from SME to large international companies. The projects are merging fundamental aspects with advanced technological and industrial developments; nanosciences are connected with material sciences, optics, electronics and micro & nano-fabrication.

| Edito                                       | 5  |

|---------------------------------------------|----|

| Key figures, awards, books                  | 7  |

| 1-Infra-Red imaging: Cooled detectors       | 9  |

| 2-Infra-Red imaging: <i>microbolometers</i> | 19 |

| 3-Optical environmental sensors             | 23 |

| 4-Silicon Photonics                         | 27 |

| 5-Solid state lighting (LED)                | 37 |

| 6-Display components                        | 47 |

| 7-Optics and nanophotonics                  | 53 |

| 8-PhD degrees awarded in 2014               | 57 |

#### Dear Reader

The Optics and Photonics Division (DOPT) of LETI is focused on a few selected photonic applications where technology and integration strongly impact the final products. The expected impact could be through decreasing the cost, improving the performances or increasing the number of functions.

Photonics is recognized as a Key Enabling Technology by the European Union and attracts a lot of interest and efforts from industrial companies and research institutions throughout the world. Staying on the leading edge of photonics requires strong relationships both with industrial partners, through one-to-one or collaborative projects, and with academic partners, through strategic alliances and collaborative projects as well.

Our strong will to build a bridge between academy and industry is illustrated in this report by several results co-authored with both kinds of organizations/companies. Furthermore, we also extend the frontiers of photonics by benefiting from the multidisciplinary environment of LETI and CEATech and their wide expertise and technological capabilities.

I hope that reading this report will make you want to know even more about us, meet us during conferences, professional forums or LETI Days, join us as a researcher, a PhD or a post-doctoral fellow and, of course, build fruitful collaborations on exciting research topics tackling the behavior of photons at small scale using up to date industry compatible facilities.

Have a nice reading!

- 185 permanent researchers

- 35 PhD students and Post-docs

- 32 CEA experts: 2 directors of research

- and 3 international experts

100 publications in 2014 including 35 papers in peer reviewed journals. One hundred of additional publications were co-authored with other divisions, universities and private companies

- 65 patents filed in 2014

- 430 patents portfolio with 20% under licence

Clean rooms dedicated to imaging & photonics fabrication, tests and component packaging.

- Optics and opto-electronics characterization facilities

- Modeling and simulation

#### **Awards**

Anthony LEFEBVRE received the award for the best student paper at the SPIE Photonics Europe conference for his presentation "Optimization of a radiative membrane for gas sensing applications"

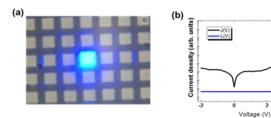

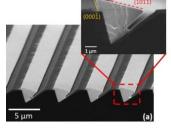

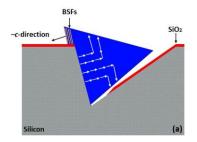

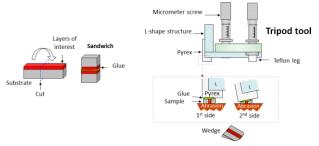

Michel KHOURY received the award for the best student paper at the SPIE Photonics Europe conference for his presentation: "Growth of Semipolar GaN on Patterned Silicon Substrates for LED Applications"

#### **Books**

- ♣ François TEMPLIER edited the book "OLED microdisplays: technology and applications" with the participation of Karim BOUZID, Tony Maindron, David VAUFREY, published by Wiley.

- Guy FEUILLET co- edited with Vincent CONSONNI (CNRS) 2 books: "Wide band Gap Semiconductor nanowires 1 and 2" with the participation of Pierre TCHOULFIAN and Pierre FERRET, published by Wiley.

### **Conferences and Workshops organization**

- Jean- Marc FEDELI with "Group Four Photonics" (Paris 2014)

- Yvon CAZAUX and Bruno MOUREY for "SEMICON" (Grenoble 2014)

# Infra-Red maging: Cooled detectors

HgCdTe Epi. growth, photodiodes design

Avalanche single photon detectors (APD)

HgCdTe focal plane arrays: SWIR, LWIR

Small pitch, hybridization, optics

## A new nBn IR detection concept using HgCdTe material

#### **Research topics: Quantum IR detection**

#### O. Gravrand, F. Boulard, Ph. Ballet, W. Hassis

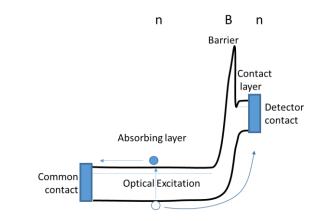

ABSTRACT: This paper presents a new HgCdTe based heterostructure to perform high performance quantum IR detection. The structure is based on the unipolar barrier heterostructure grown by MBE mimicking the valence band structure of a classical photodiode. The aim is to simplify the fabrication process, and drastically decrease the dark noise at low temperature. The concept has been studied by FEM simulation and showed promising results. First experimental characterization of the EO properties of such structures showed promising features: 60% quantum efficiency and low turn-on voltage have been measured on single pixels.

In a conventional photodiode, the minority carrier collection is done using the electric field of the p-n junction's space charge region. This electric field usually induces leakage current in the narrow gap materials used for the IR detection. We have been working on a new detection concept using a MBE grown unipolar barrier structure. The driving idea is to use the flexibility of HgCdTe (which is a narrow gap semiconductor material suitable for absorption in the IR) grown by molecular beam epitaxy (MBE) to mimic the valence band structure of a p/n photodiode while maintaining the high field into a larger band gap material (the so called barrier) thus limiting current leakage of the structure. The band gap difference between narrow and large gap has to block the flow of electron on the conduction band while facilitating the flow of holes on the valence band (see fig1). The resulting unipolar device therefore behaves like a diode and might be used for IR photovoltaic detection.

Our original barrier design makes use of graded interfaces tailored during the MBE growth in order to optimize the band diagram. This nBn detection structure is based on an asymmetrical barrier design with a uniform N type doping level through the whole structure. In this design, a graded barrier is used to manage the valence band offset and therefore facilitate the flow of minority carrier thru the structure thus optimizing the quantum efficiency of the resulting detector.

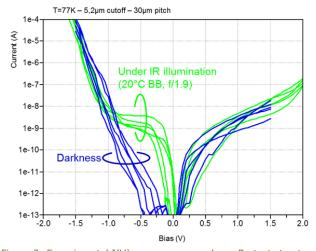

The valence band residual barrier (and the associated turnon voltage) is managed using a graded barrier interface on the absorbing layer side. This interface has to remain as abrupt as possible on the contact side to get the highest effective barrier on the conduction band, therefore limiting thermionic currents. This structure has been extensively studied by FEM simulation to get the optimal design profile, best tradeoff between diffusion turn on voltage, GR bias and thermionic currents. At last, this structure has been grown by MBE and processed into  $30\mu m$  pitch nBn pixels. Test chips hybridized on Silicon fanouts and backside illuminated demonstrated good detection performances. However, SIMS analysis showed that the grown layer composition profile was different from the targeted barrier profile. The contact layer has a larger gap and the barrier contact interface was not as abrupt as estimated. As a consequence, experimental IVs showed stronger thermionic currents than previously computed. Yet, low diffusion turn-on voltages have been observed. Experimental bariodes exhibited 60% QE, with diffusion limited spatial behavior.

Last but not least, measured spectral responses showed expected triangular response shapes, indicating a uniform QE on a large spectral band.

The work opens the gate to high yield in the fabrication of ultra-low dark current focal plane arrays in the IR range.

Figure 1 : Principle of the barrier structure (nBn)

Figure 2: Experimental I(V) curves measured on nBn test structures

#### Related publications:

<sup>[1]</sup> O. Gravrand, F. Boulard, A. Ferron, Ph. Ballet, W. Hassis, "A new nBn IR detection concept using HgCdTe material", to be published in Journal of Electronic Materials 2015 [2] L. Lolis, T. Ayed, C. Bernier, M. Pelissier, D. Dallet, J. B. Bégueret, "Ultra Low Power Bandpass Sampling Architectures Using Lamb Wave Filters", IEEE NEWCAS, 2010.

<sup>[2]</sup> W. Hassis (2014). "Etude de structures avancées pour la détection IR quantique à haute température". Thèse Université de Grenoble

# Study of systemic 1/f noise in HgCdTe IR photodiodes operated at high temperature

#### Research topics: Quantum IR detection, flicker noise

#### O. Gravrand, J. Rothman, W. Hassis

ABSTRACT: The narrow band gap on which IR detection relies requires cooling of focal plane arrays to cryogenic temperatures. In practice, increasing the operating temperature (for power issues of future portable detectors) leads to an increase in low frequency noise of the photodiodes leading to performance degradation. Therefore 1/f noise has been investigated on a very large set of IR HgCdTe photodiodes with different gaps, different dopings and various temperatures. The results of this study are trends for future optimization for high operating temperature focal plane arrays.

The dark current of IR photodiodes is highly depending on operation temperature. As a consequence, the operating temperature is usually very low, down to cryogenic temperatures for MWIR range (up to 5  $\mu m$  wavelength) and LWIR (up to  $10\mu m$ ). However, today trend is to operate those detectors at higher temperatures and it appears that the first limiting parameter is the appearance of 1/f at high temperatures, rather than the dark current shot noise. This effect limits in fact the noise defect rate of focal plane arrays at lower temperatures than expected from the calculated dark current values and must be therefore deeply investigated.

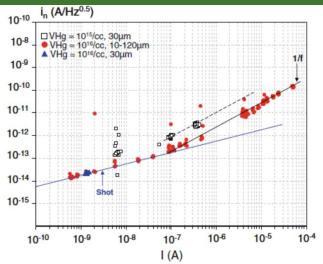

We studied 1/f noise in MWIR and LWIR VHg-doped n+/p photodiodes with different geometries, epitaxial layer thicknesses, and doping concentrations. Contrasting 1/f noise behavior was observed in diodes operating in the different wavelength ranges. Noise measurements performed on MWIR photodiodes revealed a new type of 1/f noise mechanism, in which the noise was directly proportional to the total current generated inside the effective photodiode area. This previously unobserved type of 1/f noise is generated in the bulk of the photodetector and has an area dependence that may be explained by the modulation of the diffusion current amplitude, which itself increases with the square of the distance to the junction. This new 1/f noise mechanism led us to the development of a phenomenological relation that is reminiscent of the 1/f Hooge model. This relation involves an experimental constant, which we supposed to be related to a volumetric defect density. For LWIR photodiodes, it was found that the noise current density is independent of the diode area at constant temperature, contrary to the behavior observed in MWIR diodes (scaling with A) and also different from that expected according to the various models, which scale with A^1/2 or A^1/4. The increase of the noise current density due to the increase in temperature revealed that the noise is due to the modulation of a quantity that is proportional to the diffusion current generation rate, i.e., to ni<sup>2</sup>. The origin of this modulation seems not to be related to the diode geometry. The modulation of the space charge region at the junction singularities at the corners of the square diode implants may be the origin of this interesting behavior.

Figure 2: Noise measurements of MWIR n+/p LPE photodiodes with Different doping concentrations.

Figure 3: Normalized Noise current density versus total current for HgCdTe diffusion-limited diodes.Noise measurements of MWIR n+/p compared between different manufacturing companies

#### Related publications:

<sup>[1]</sup> Hassis, W., Gravrand, O., Rothman, J., & Benahmed, S. (2013). "Low-Frequency Noise Characteristics of HgCdTe Infrared Photodiodes Operating at High Temperatures. Journal of Electronic Materials", 42(11), 3288–3296.

<sup>[2]</sup> Gravrand, O., Destefanis, G., Bisotto, S., Baier, N., Rothman, J., Mollard, L., Vuillermet, M. (2013). "Issues in HgCdTe Research and Expected Progress in Infrared Detector Fabrication". Journal of Electronic Materials, 42(11), 3349–3358.

<sup>[3]</sup> Hassis W. (2014). "Etude de structures avancées pour la détection IR quantique à haute température". PhD Dissertation Université de Grenoble

# Sub-wavelength photonic structure to add spectral capabilities to MWIR HgCdTe photodiode

F. Boulard, O. Gravrand, L. Adelmini, D. Fowler, G. Badano, P. Ballet, M. Duperron, R. Espiau De Lamaestre

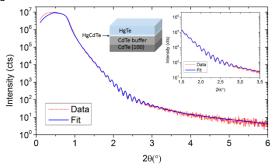

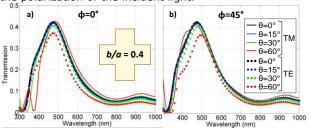

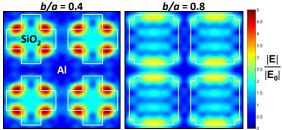

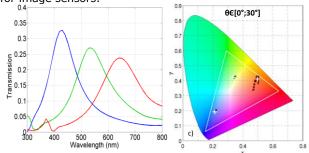

ABSTRACT: we present simulation and experimental results on the design and integration of sub-wavelength photonic structures to add spectral functionalities to MWIR HgCdTe photodiodes. The relationship between the metallic grating design and the excited optical mode is illustrated using numerical simulations. The agreement with the measured spectral response and dispersion relation on a test photodiode array is discussed. Finally, first results from a MWIR FPA are presented with operability as high as 99.7%.

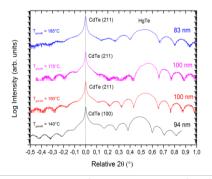

During the last decades, thanks to its tunable band gap and small lattice parameter variation, multispectral Mercury Cadmium Telluride (MCT) heterostructures have been grown and processed to cover the whole IR range from short to long wave infrared, with intra or extra-band detection[1]. However, this approach is based on complex heterostructures with deep etching requirements increasing growth [2] and processing challenges [3] on small gap materials. Suitably designed metal dielectric nanocavities are promising candidates to add spectral capabilities on planar absorbers [4]. This paper presents experimental results on the integration of such a sub-wavelength photonic structures. Molecular beam epitaxy mid-wave MCT layers are grown on CdZnTe substrates. Diodes are fabricated following standard n on p (vacancy doped) technology while a specific e-beam lithography and etch step is added to define metal dielectric

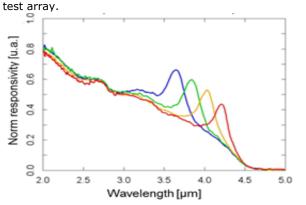

nanocavities inside the passivation layer. Specific care is taken to minimize field stitching misalignments since the focal plane array area is larger than the electron beam field. After processing, diodes arrays were hybridized on a silicon fan-out and characterized at 77K. Fig 1 shows a normalized

spectral response on a backside illuminated MCT photodiode

Figure 1 : Normalized spectral response of 4 colors MWIR HgCdTe photodiode test array

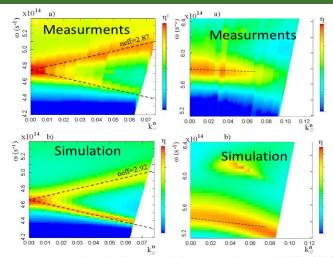

Tuning the nanocavitiy periods allows the spectral control of the responsivity enhancement. However, in such a design, the absorption wavelength maximum exhibits a strong dependence on the light incidence angle, as shown by the resonance splitting on the simulated (RCWA) and experimental dispersion diagram on the left side of fig2. An improved design allowing larger angular acceptance (fig 2, right) is implemented on a four color MWIR QVGA (320 x 256) 30  $\mu m$  pitch FPA, with various pixel design on 160x128 subareas.

Figure 2 : Simulated and measured dispersion diagram (w,k//) of (left) diffractive and (right) hybrid IR incoming light coupling with HgCdTe absorber.

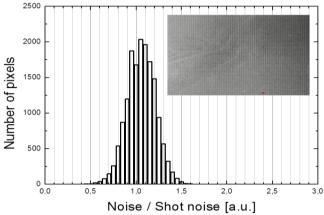

Under typical test conditions ( $T^\circ=77K$ ,  $FOV=30^\circ$ , C=2,1pF, Tint5.5ms,  $T^\circ bb=300K$  and 310K), the pixel responsivity check pattern (fig3 inlet) underlines the spectral capabilities given by the addition of the photonic structure. An FPA noise histogram is compared to theoretical shot noise on fig 3. The distribution is centered on 1 without a tail, representing excellent operability ( $\pm50\%$  criterium) greater than 99,7%, and demonstrating the process quality, from MCT layer growth to color device processing.

Figure 3 : Noise to shot noise ratio histograms and responsivity mapping (inlet) of 4 colors 30  $\mu$ m pitch MWIR 128x160 FPA at 77K

Related publications:

[1] J. Baylet, et. al., Study of the pixel-pitch reduction for HgCdTe infrared dual-band detectors, J. Electron. Materials, 33 (6) (2004). [2] P. Ballet, et.al., Dual-band infrared detectors made on high-quality HgCdTe epilayers grown by molecular beam epitaxy on CdZnTe or CdTe/Ge substrates J. Electron. Materials, 33 (6), 667-72 (2004).

[3] F. Boulard, J. Baylet, C. Cardinaud, Influence of cadmium composition on CH 4-H 2-based inductively coupled plasma etching of Hg 1-xCd xTe J. Electron. Materials 39 (8), 1256-61 (2010).

[4] D.Fowler & al. Partially localized hybrid surface plasmon mode for thin-film semiconductor IR photodetection Optics Letters 38 (2013)

# Very-long wavelength infrared detection with HgCdTe for space applications

#### N. Baier, O. Boulade\* (\* CEA/ IRFU/ SAP)

ABSTRACT: New technological design and improved growth process of HgCdTe have been evaluated to determine performances of p/n photodiodes in specific conditions. For space applications, long cutoff wavelength (up to  $17\mu m$ ) and very low dark current (low light flux conditions) are required. Quarter VGA format focal plane arrays have been tested and exhibit good performances:  $17.2\mu m$  cutoff and state-of-the art dark current at 78K has been obtained with high operability (<0.1% defects) and homogenous mapping. Dark current reference model in literature has been revisited at low temperature (>20K) with these results.

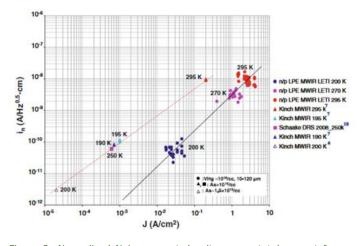

The p-on-n photodiodes architecture relies on an In-doped HgCdTe active base layer grown on a lattice matched CdZnTe substrate by horizontal-slider Liquid Phase Epitaxy (LPE). This process grants a homogenous cadmium composition, critical in the very-long wavelength IR spectral band as a small variation in composition will result in a large variation of cutoff wavelength. p-on-n junction is made with ion implantation of As.

A new heterojunction process has been evaluated [1], designed to reduce depletion dark current (typically generation-recombination) and the temperature at which this kind of current becomes larger than diffusion current. Moreover, this heterojunction places interface between active layer and passivation in a larger bandgap, thus lowering the defects impact on performances (operability and homogeneity). The challenge here is to control the depth of the LPE heterojunction as if it is placed too deep, it may result in the formation of a potential barrier which will lower the quantum efficiency.

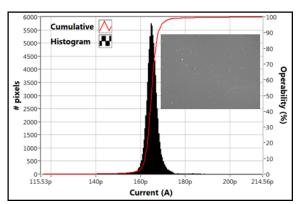

Two sets of detectors have been manufactured. The first one has a cutoff wavelength of 17.2µm at 78K, highest value obtained on this kind of structure in literature. Focal plane array (quarter VGA format) operability is 99.7% and quantum efficiency near 70%. Electronic noise is limited by photon noise. Dark current density is at the state of the art.

Figure 1: Photonic current histogram and mapping obtained on quarter VGA format array.

The second set of detectors has been manufactured to fulfill specific requirements for space astrophysics: low flux detection at low operating temperature (to reduce dark current).

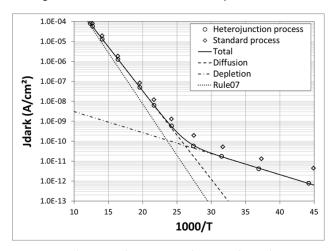

Cutoff wavelength is 12.5µm at 40K. Operability is over 99.9%, the best result has been obtained on an array with heterojunction process, better than with standard homojunction process. This new process shows its benefits in terms of stabilization of photodiodes performances. Quantum efficiency is above 80%. Dark current tends to be in good agreement with "Rule07" model at 78K [Tennant, W.E & al," Journal of Electronic Materials 37 (9) (2008)].

This heuristic model is a reference for p-on-n HgCdTe infrared detectors. However, at lower temperatures, results measured on arrays presented above and on other ones realized by different manufacturers [McMurtry, C. & al, Optical Engineering 52 (9), 091804-1 (2013)] are not following this model. The dark current tends to vary with a pure diffusion model with the temperature down to 42K, reaching 6  $10^{-10}$  A/cm². At this point, the dark current is limited by another regime, based on a depletion current behavior with an ideality exponential factor of 4.2. At 23K, dark current is 8  $10^{-13}$  A/cm² (45 electrons/s in a pixel of  $30\mu m$  pitch). This results meets the requirements given for space applications low flux detection.

Further investigations will be done on new detectors to understand the origin of the limiting current regime at low temperature. With improvements of the process, we may manage to decrease this transition temperature.

Figure 2: Dark current densities as a function of 1000/T. Comparison between measurements and models.

Related Publications:

[1] Baier, N. et al., "MCT planar p-on-n LW and VLW IRFPAs," Proc. SPIE 8704, 87042P (2013)

## Demonstration of a 10µm pixel pitch XGA HgCdTe focal plane array

S.Bisotto, F.Marion, M. Volpert, F.Guellec\*, Y. Reibel\*\* (\*LETI/DACLE, \*\*Sofradir)

ABSTRACT: Small pitch large focal plane arrays are now available in HgCdTe technology, 15 $\mu$ m being the standard industrial pitch; academic studies have proved a potential benefit provided by going to smaller pitches, as far as 5  $\mu$ m.

The  $10\mu m$  pitch XGA demonstrator presented here is a n-on-p HgCdTe HOT technology focal plane array operating in the mid-wave infrared (MWIR).

The overall development has been carried out with Sofradir, french IR detectors manufacturer. A first demonstration of the Sofradir device was performed at Baltimore SPIE 2014.

Reducing the pixel pitch and increasing the focal plane array size are two conjugate tendencies that have proven to have benefits, not only in producing very compact products, but also in providing a better image resolution [2] without degrading NETD and pixel operability at high temperature. Considerable efforts have been carried out at LETI and Sofradir in technology improvement in order to solve the related issues, more particularly the noise operability for HOT operation, as well as hybridization techniques at small pitches [3]. The 10µm pitch pixel takes advantage from these studies, with a reduction on dark current, and an increase in operating temperature over 110K.

The development of this demonstrator has been carried out by Sofradir and LETI. The difference between the two approaches resides mainly in the hybridization technique. The standard Sofradir process is based on indium microbumps formed on the Si ROIC (Read Out Integrated Circuit) side; Sofradir has presented a demonstrator at Baltimore SPIE 2014 prefiguring Sofradir's DAPHNIS line [1].

An alternative low thermal budget process, working at room temperature, is developed by LETI, and is especially suitable for ultra-small pitch. The LETI demonstrator is the first HgCdTe large array successfully hybridized with this technique. A 2kx2k 10 $\mu m$  pitch HgCdTe mechanical demonstrator is expected this year.

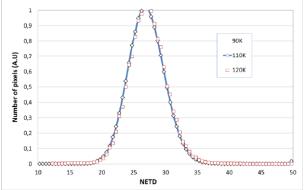

The pixel architecture is based on a DI stage, with a 2Mewell. The ROIC enables to read out  $1024x768\ 10\mu m$  pitch photo diodes, in snapshot mode, up to 20MHz. The integration mode is either integrate-then-read (ITR) or integrate-while-read (IWR), and the operational temperature is 90K to 130K.

The power consumption is kept low thanks to circuitry implemented in dual analog-digital threshold voltages. It has been measured at 80mW at 10MHz (102 nW/pixel).

The electro-optical performances of the demonstrator are quite good: at an aperture of F/#2, the NETD at 50% well fill is 26mK at 110K (see figure 1) and remains stable up to 130K. The residual fixed pattern noise (RFPN) is below the temporal noise.

Figure 1: NETD at 50% well fill Tpf=110K from the Sofradir device

The LETI hybridization process enables an excellent operability with an exceptional reliability: after ageing for 15 days at  $80^{\circ}$ C and 2000 thermal cycles from +20°C to -180°C, the operability is 99.99% for opens and the short rate is 0.035%. Moreover the electro-optical performances remain unchanged.

Figure 2: IR image from the LETI demonstrator

#### Related Publications :

<sup>[1]</sup> Y. Reibel, N. Pere-Laperne, T. Augey, L. Rubaldo, G. Decaens, ML. Bourqui, A. Manissadjian, D. Billon-Lanfrey, S. Bisotto, O. Gravrand, G. Destefanis, G. Druart, N. Guerineau: "Getting Small, new 10µm pixel pitch cooled infrared products", Proc. Of SPIE Vol. 9070, 2014 [2] O.Gravrand, N.Baier, A. Ferron, F. Rochette, J. Berthoz, L. Rubaldo, R. Cluzel: "MTF Issues in Small-Pixel-Pitch Planar Quantum IR Detectors", Journal of Electronic Materials 10.1007/s11664-014-3185-3, 2014

<sup>[3]</sup> O. Gravrand, G. Destefanis, S. Bisotto, N. Baier, J. Rothman, L. Mollard, D. Brellier, L. Rubaldo, A. Kerlain, V. Destefanis, and M. Vuillermet: "Issues in HgCdTe Research and Expected Progress in Infrared Detector Fabrication", Journal of Electronic Materians, vol. 42, n° 11, pp. 3349-3358, 2013

## 3D modeling of Flip-Chip assemblies

#### Research topics: Flip-Chip, 3D numerical simulation, high count ball grid array

W. Kpobie, P. Lipinski\*, N. Bonfoh\*, M. Fendler, C. Dreistadt\* (\* ENIM, Metz, France)

ABSTRACT: we present an original approach for 3D numerical simulation of fine-pitch high-count ball grid flip-chip assemblies. With the increase of the resolution of imagers, the interconnection layer of flip-chip assembly includes more than 1 million solder micro-balls (10  $\mu$ m in diameter) at fine pitches down to 10  $\mu$ m and the optimization process of such structures through numerical simulations turns out to be a very time-consuming task. For such configurations, we propose an alternative approach, which consists in replacing this heterogeneous interconnection layer by a homogeneous equivalent material (HEM) which thermomechanical properties are determined by using homogenization methods.

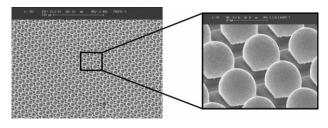

The most sensitive area of a flip-chip electronic assembly is the interconnection layer, which, for example, in the case of an infrared detector, connects the readout and detection circuits (each being about 500  $\mu m$  thick). This heterogeneous layer is composed of a very large number (over one million) of solder bumps with small dimensions (about 10  $\mu m$  diameter), with or without adhesive (e.g., epoxy) underfill (Fig. 1). Numerical modeling of such a structure may generate a large number of degrees of freedom and requires the use of powerful supercomputers. Faced with this problem, we proposed an original approach, which consists in replacing this interconnection layer (solder bumps embedded in an epoxy matrix) by a macro-HEM. For this purpose, thermoelastic homogenization schemes can be used to estimate the effective properties of such a fictitious HEM.

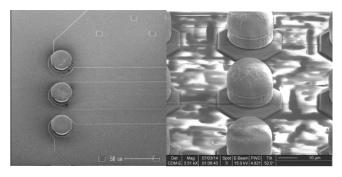

Figure 1 : Fine-pitch (15 μm) indium microbumping

To take into account the thermomechanical interactions between the local phases of this heterogeneous interconnection layer, multisite micromechanical modeling (Mori-Tanaka approximation) of the effective thermoelastic properties of heterogeneous materials, based on the corresponding general thermoelastic integral equation, has been proposed [1].

The developed micromechanical model was then implemented in the finite-element code Abaqus Standard via the user subroutine UMAT.

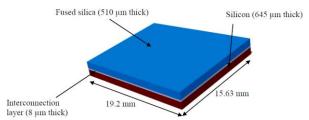

The considered flip-chip assembly for a megapixel array consists of 1280  $\times$  1024 bumps at 15  $\mu m$  pitch (Fig. 2).

Figure 2: Description of the assembly studied

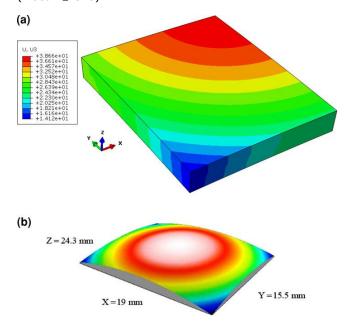

Predictions of the implemented model with the HEM are analyzed in terms of the vertical displacement as depicted in Fig. 3a. The corresponding maximal deflection on the fused silica surface is about 24.2  $\mu$ m. This simulated result is compared with experimental measurements (Fig. 3b), carried out with an optical chromatic confocal surface analyzer (Altisurf© 520).

Figure 3 : Vertical displacement U3 ( $\mu$ m): (a) megapixel model and (b) experimental deflection measured on a megapixel dummy sample (fused silica/silicon substrates)

These measurements were performed on six samples of the megapixel flip-chip assembly. For these tested samples, the measured vertical deflection is distributed between 19.4  $\mu$ m and 24.3  $\mu$ m (with average of 21.53  $\mu$ m). The relative error between the results of the numerical simulation and the experimental measurements is less than 12.4% [2].

To estimate the stress and strain fields in the indium bumps, submodeling was used for structural zoom. Applied to a megapixel-format assembly, it revealed that local stresses are maximal in the vicinity of the interfaces between solder bumps and the chip. Cracks are therefore expected to initiate in this area of the flip chip because of the presence of IMC formed during soldering.

#### Related Publications :

[1]W. Kpobie, S. Ben Khlifa, N. Bonfoh, M. Fendler, and P. Lipinski, "Multi-site micromechanical modelling of thermo-elastic properties of heterogeneous materials," Compos. Struct., vol. 94, no. 6, pp. 2068–2077, 2012.

[2]W. Kpobie, N. Bonfoh, C. Dreistadt, M. Fendler, and P. Lipinski, "Three-Dimensional Thermomechanical Simulation of Fine-Pitch High-

[2]W. Kpobie, N. Bonfoh, C. Dreistadt, M. Fendler, and P. Lipinski, "Three-Dimensional Thermomechanical Simulation of Fine-Pitch High-Count Ball Grid Array Flip-Chip Assemblies," J. Electron. Mater., vol. 43, no. 3, pp. 671–684, 2014.

## Overview of curved and flexible image sensors at LETI

#### Y. Gaeremynck, E. Hugot, K. Tekaya, A. Vandeneynde, A. Gueugnot

ABSTRACT: we present an overview of developments in curve and flexible image sensors based on CMOS chips. A first part presents applications, with a focus on a wide field imaging system currently under fabrication. Second part presents results obtained for infrared sensors as well for micro-bolometers as for sorted autosum sensors, last port details for infrared sensor for visible wave length, the assembly of this sensor is under patent procedure.

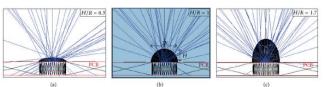

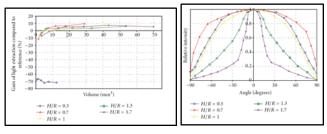

The emergence of curved detectors, first proposed by Ko et al in their Nature paper [Ko et Al. Nature (letters), 454, 748-753, 2008], certainly represents the major disruptive technology for imaging systems that will come up in a near future. This technology is very versatile and can be integrated to enhance existing systems as well as to allow full new applications.

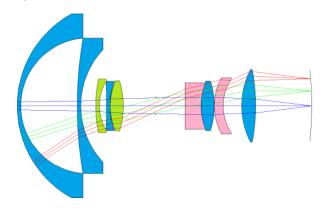

For example in existing systems, it is possible to simplify imaging system and enhance image definition as we compensate Petzval field curvature with the image sensor. Petzval field curvature is one of the main optical aberrations, it affects in particular wide field imaging systems. That is why we demonstrated competitive advantage of this technology on a fish-eye zoom. With comparable performances as a patented 8-15 mm/4 professional Canon zoom [Okumura T. & al, patent EP 2407809A1], the introduction of curved sensor allowed a reduction of necessary lenses, from 14 to 9, glass types, from 11 to 3 and suppressing the 2 aspherical surfaces. We notice far better optical tolerances with sensitivity to defects divided by 4. This optical system has been fabricated to makes a first full optimized optical system using curved sensors. The system will be full characterized in coming months.

Figure 4: side view of simplified fish-eye imaging system. The simplification of optical design is obtained thanks to introduction of curved sensor.

A second example for innovative systems, curved sensors allow also innovative systems like wide field multi-pupillar systems. In this case by taking advantage of the curvature of the sensor, the introduction of micro-prism matrix becomes obsolete.

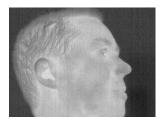

First results of curvature were obtained by D. Dumas and M Fendler [1].

They realized spherical and cylindrical shapes both on micro bolometers and cooled infrared detectors. In all cases the chip is thinned to reach less than 100 µm of thickness. Under this condition, we get fully operating micro-bolometer chip of 1 cm² up to a spherical curvature radius of 80 mm. these chips are made of full silicon. The team performed the same process of curvature on hybrid cooled infrared arrays. These arrays are composed of silicon and CdHgTe chips Notice that CdHgTe is a very brittle material that implies high difficulties to curve it. Nevertheless, we also reach 200 mm spherical curvature radius and 100 mm cylindrical curvature radius. These sensors performed image shots at 80 K attesting the operability [2].

Figure 5 : Picture obtained with spherical curved cooled infrared  $\overline{\text{CMOS}}$  array.

Based on these good results, we carry on developing a very reproducible curvature system, allowing also adjustable radius of curvature of the sensor. In a partnership with LAM (Laboratoire d'Astrophysique de Marseille) we developed 3D printed carrier adapted to images sensors. These carriers are the results of finite element simulations; in addition to image sensor the assembly is currently under patent procedure.

This work has been partially supported by the LabEx FOCUS ANR-11-LABX-0013 and DGA.

#### Related Publications

[1] D. Dumas & al" Curved focal plane detector array for wide field cameras » applied optics (51) 22, 2012

[2] K. Tekaya et Al. "Hemispherical curved monolithic cooled and uncooled infrared focal plane arrays for compact cameras" DSS SPIE, 90702T, 2014

## High operating temperature SWIR HgCdTe APDs for remote sensing

#### Research topics: High sensitivity photo detection, avalanche photodiodes, LIDAR

J. Rothman, Foubert, K., Lasfargues, G., Largeron, C., Zayer\*, I., Sodnik\*, Z., Mosberger\*, M., Widmer, J.\* (\*European Space Agency, ESA)

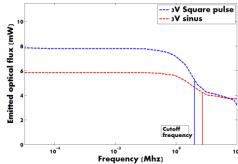

ABSTRACT: Large area high operating temperature HgCdTe avalanche photodiode detector modules have been developed for remote sensing of gazes and free space optical telecommunications. The detectors with an active optical diameter of about 200  $\mu$ m are cooled in a dedicated vacuum packaging using thermo-electric cooling (TEC) to operating temperatures around 200 K. The use of HgCdTe APDs with high linear gain and low excess noise factor made it possible to achieve record high sensitivity for such versatile detectors, with noise equivalent powers of 30 fW/ $\sqrt{\text{Hz}}$  for bandwidth ranging between 20 and 300 MHz.

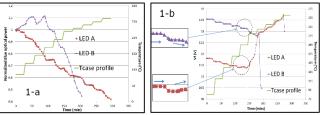

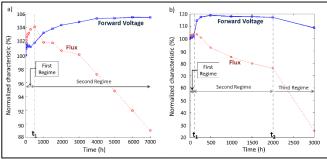

HgCdTe APDs have been shown to exhibit close to optimal amplification properties characterized by an exponential increasing linear gain as a function of reverse bias, up to multiplication factors higher than 1000, close to negligible excess noise and a response time which is not dependent on the gain. These characteristics have opened new perspectives in most fields of low photon number detection at wavelengths reaching from the UV to the Infra-Red (IR) detector cut-of wavelength. The high performance of HgCdTe APDs is principally due to multiplication through impact ionization which is exclusively initiated by the electrons. All laboratories capable of making functional HgCdTe APDs are mainly focused on imagery. This fact concentrated the first developments of detector modules on high performance focal plane arrays. However, a large number of applications, such as remote sensing using LIDAR and free-space optical telecommunications (FSO) do the measurement of the temporal variation of the photon-flux on a single element detector. The detectors described in this paper are the result of the first efforts at Leti, supported by a Carnot project and by CNES and ESA, to develop such detectors based on a versatile and potentially low cost approach.

The required temporal resolution in most LIDAR and FSO applications ranges between 50 ns to 250 ps, corresponding to bandwidths between 10 MHz and 2 GHz. The active optical diameter depends on the receiver optics and is typically in the range of 80 to 200  $\mu m$ . These specifications define the parameter space in terms of Cd composition, operating temperature, sensitivity and active area. The sensitivity is ultimately limited by the dark noise of the APD, induced by the dark current and residual thermal flux. The noise of these contributions should be lower or equal to the input referred noise of the pre-amplifier. In the present development, we have chosen to work with detectors cooled down to temperatures around 200 K. This allows using thermo-electric cooling (TEC), in ground based applications, or passive cooling, in space applications. In order to obtain the lowest possible temperature and largest optical active area, we have chosen to deport the amplifier off the cold-down surface rather than to hybridize the APD on the amplifier. This choice implies a higher amplifier noise which needs to be overcome by a higher APD gain. This choice enables a lower operating temperature of the APD and is versatile, as it allows changing the APD cut-off wavelength and surface with a given amplifier and/or the amplifier with a given APD as a function of application requirements. The performance of the detector module can be predicted taking into account the TIA noise, the expected APD dark current and residual thermal radiation [1]. We have shown that the equivalent input noise reaches values below 10 photons per characteristic time for the aimed operating temperature and detector areas. Such sensitivities open a new horizon of applications which requires resolving

the temporal variation of faint IR signals, such as LIDAR, FSO and range finders.

Figure 1 : Photography of the inside of a HgCdTe APD detector module.

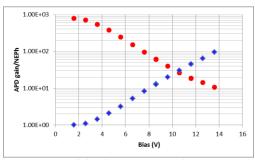

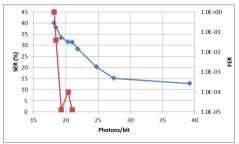

Figure 1 shows a photograph of the detector assembly. A large packaging has been used that allows keeping the TIA inside the packaging to reduce the influence of parasitic impedances and RF noise pick-up. At present, we have developed two detector modules using a low BW TIA (20 MHz for LIDAR detection of greenhouse gases, with CNES), and a high BW TIA (300 MHz for FSO with ESA or range finding). Figure 2 illustrates the measured gain and equivalent input noise of the high-bandwidth detector. At a gain of 100, the equivalent input noise is close to 10 photons. At this limit, the detector noise generated by the detection of residual IR light starts to limit the sensitivity and lower noise can be achieved using optical filters. Nevertheless, this value corresponds to a record low noise equivalent input optical noise (NEP) of 34  $fW/\sqrt{Hz}$ . An equally record low NEP of 30  $fW/\sqrt{Hz}$  was measured on the lower BW detector [1]. The next step of the present development is the space qualification of the LETI HgCdTe APD technology, in collaboration with CNES, and the optimization of the APD bandwidth for high data rate FSO.

Figure 1 : Variation of the detector gain and input equivalent photon noise of the high BW detector module developed for FSO in collaboration with ESA

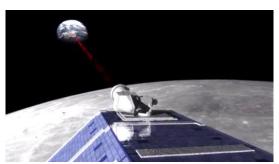

# Lunar Laser Communication Demonstration (LLCD) using HgCdTe APDs

# J. Rothman in collaborration with European Space Agency (ESA) and the German Aerospace Center

ABSTRACT: This paper presents the results of the Lunar Laser Communication Demonstration using a receiver module made with a large area HgCdTe APD detector manufactured at CEA/Leti. The receiver was used to detect and decode a position pulse modulated (ppm) 40 and 80 Mbit/s signal emitted from Nasas Space craft LADEE. Error free data transfer was demonstrated for both modes when the average power corresponded to more than 40 photons per laser pulse. Gbps data transfer rates can be expected in detector modules with optimized sensitivity and bandwidth.

Figure 1 : Illustration of the laser emission of PPM data from the LADEE space craft, orbiting the moon, to earth ©Nasa.

Free space optical communications is considered to be a key enabling technology to access data at high rate both from satellites orbiting the earth and for deep space mission beyond the moon. The interest in FSO is motivated by the capacity to send data higher rates than in radio communications using smaller and lighter components which consume less. In addition and in opposite to the crowded radio spectrum, the IR spectrum is free of use for commercial applications. The Lunar Laser Communication Demonstration was launched by Nasa in 2008 to demonstrate the maturity of FSO for very long range high data rate laser communications to and from the moon [1]. ESA joined the project in 2011, with the aim to evaluate the maturity of commercially existing components for long range FSO. CEA/Leti joined the project in the beginning of 2013, when ESA concluded on the lack of detectors which could decode the faint signals at high speed. Thanks to a development already undertaken in an internally funded CARNOT program, we were able to deliver in time for the LLCD demonstration a detector module with a bandwidth (80 MHz) associated with a record low noise equivalent power (NEP) of 0.59 nW [2].

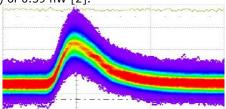

Figure 2 : Impulse response of a 160  $\mu$ m diameter APD coupled with TIA-1, operated at T=190 K with a gain of M=95 to an impulse of 100 photons. The vertical and horizontal scales are 5 ns and 10 mV per division, respectively.

The data emitted from the moon was encoded using 16ary pulse position modulation (PPM) with pulse durations from 3.2 ns (Mode 5, decoded transmission rate of 39 Mbits/s) down to

0.2 ns (Mode 1, decoded transmission rate of 625 Mbits/s) by modulating a CW laser with an average power of 0.5 W. The expected average power on the detector is around 300 pW, corresponding to about 120 photons per pulse during Mode 5 modulation. Fig. 2 illustrates the response of the detector to this signal level in the lab. At this power the signal is much larger than the noise and an error free detection can be expected.

The performance of the APD detector module was first tested as a function of input average power using laboratory generated Mode 5 and Mode 4 modulated light. Fig. 3 reports the variation of the symbol and decoded frame error rate as a function of the average power on the detector. Error rates below 10<sup>-5</sup> were achieved for average optical power down to 100 pW, which corresponds to 20 photons per decoded bit in mode 5. Due to bandwidth limitations of the detector, the mode 4 required higher optical power, at least 200 pW to achieve error rates below 10<sup>-5</sup>. A stable error free Mode 5 (40 Mbits/s) down link was first demonstrated on 3/4/2014 for an operation lasting over 9 minutes. A Mode 4 down link (80 Mbits/s) was demonstrated later the same day.

The data obtained at OGS should be compared with the results obtained by NASA using super-conducting nanowire single photon detectors (SNSPD operated at 2 K), which have been optimized for LLCD by the Lincoln lab at MIT [1]. Error free down-link connexion was demonstrated even in mode 1 (625 Mbits/s) for average signal levels down to 2 photons per pulse [D.M. Boroson et al., Proc. SPIE 8971 (2014) 89710S]. To compete with this performance we need to improve the sensitive and the bandwidth of the HgCdTe APD detectors. Our measurements have shown that 10 GHz BW should be improved with HgCdTe APDs detectors and the sensitivity can be increased by the hybridization of the APD on a CMOS circuit [1]. These perspectives imply that HgCdTe APDs are strong candidates for space and ground based Gbit/s FSO.

Figure 3: Mode 5 Symbol error rate (SER) and frame error rate (FER) as a function of the number of photons per decoded bit after error correction.

#### Related Publications :

[1] Zayer, I, J. Rothman et. al., Lunar optical communications link (LOCL) demonstration between NASA's LADEE spacecraft and ESA's optical ground station, Int. Conf. on Space Operations, SpaceOps Proc. 2014, (2014)

# Infra-Red imaging: Microbolometers

Room temperature IR detectors

Multispectral: IR to THz range

Focal plane arrays: small pitch

Pixel Level Packaging arrays

# Latest improvements in microbolometer thin film packaging: paving the way for low cost consumer applications.

J.J. Yon. G. Dumont. V. Goudon. S. Becker. A. Arnaud and S. Cortial\*. C.L. Tisse\* (\*ULIS)

ABSTRACT: Silicon-based vacuum packaging is a key enabling technology for achieving affordable uncooled Infrared Focal Plane Arrays (IRFPA) required by a promising mass market that shows momentum for some extensive consumer applications; such as automotive driving assistance, smart presence localization and building management.

Among the various approaches studied worldwide, CEA, LETI in partnership with ULIS is committed to the development of a unique technology referred to as PLP (Pixel Level Packaging). In this PLP technology, each bolometer pixel is sealed under vacuum using a transparent thin film deposition. As a result, PLP operates as an array of hermetic micro caps above the focal plane, each enclosing a single microblometer.

Over the last 20 years, the uncooled microbolometer IRFPA technology has plainly emerged in the infrared (IR) imaging business. Most current products cover the pixel range from 160x120 to 1024x768 with a pitch as low as  $17\mu m$  [1] [2]. More recently, the success of the microbolometer technology has attracted new interest for IR sensors of lower resolution for addressing a large set of smart applications that cannot comply anymore with conventional PIR-based motion sensors because of their very limited pixel count and sensitivity.

Fig. 1: PLP architecture. Schematic view (left); SEM top view (center); SEM cross section view (right)

However, the cost target for these new markets imposes the need for a technological breakthrough, mainly in regard to the vacuum packaging which remains an adverse cost driver for the microbolometer technology. In this context, CEA, LETI has been involved for several years in the development of such a disruptive packaging technology referred to as PLP (fig. 1). Toward this objective, CEA, LETI and ULIS have been developing a PLP-based thermal IR sensor with a resolution of 80x80 pixels featuring the right performance-cost tradeoff for the targeted applications.

Typical performance for 80x80 PLP-IRFPA is reported below in Table1. Its performance is compared to the one obtained from a previous development carried out on a 320x240 PLP-based IRFPA [3]. Both PLP-IRFPA feature a pixel pitch of  $34\mu m$ .

| Performance    |                                                      |

|----------------|------------------------------------------------------|

| QVGA (320x240) | (80x80)                                              |

| 34µm           | 34µm                                                 |

| 8-14µm         | 8-14µm                                               |

| 60Hz           | 120Hz                                                |

| 10.2mV/K       | 14.3mV/K                                             |

| 77mK           | 73mK                                                 |

|                | QVGA (320x240)<br>34µm<br>8-14µm<br>60Hz<br>10.2mV/K |

Table 1: PLP-IRFPA performance characteristics (2 different formats)

All measurements are performed at room temperature with F/1 optical aperture and integration time of  $65\mu s$ . The frame rates are 60Hz and 120Hz, respectively to comply with the format of each PLP-IRFPA. The IR responsivity is calculated from the output signal measurements with respect to the flux delivered by two blackbodies set at 293K and 303K respectively.

the use of a germanium frontal window whose both sides are coated with an antireflective film.

For both formats, the PLP-IRFPA exhibits high responsivity as an evidence that a high vacuum level is reached. NETD values are around 75mK and fully in line with the product requirement (<100mK).

To push forward the technology, much effort was devoted to improve its robustness and yield. The technology has currently achieved excellent repeatability, high uniformity along with pixel operability typically better than 99.7%. These results translate into high image quality. Figure 2 shows a comparison of IR images obtained from the two products (at 50Hz, with F/1 optics)

Fig 2: PLP infrared imaging ability. QVGA IRFPA (left); 80x80 IRFPA (right) with a pitch of  $34\mu m$

The right IR image in figure 2 features 80x80 pixels with a bad pixel rate as low as 0.27%. It should be emphasized that bad pixels are only related to electrical defects, without any occurrence of vacuum defects. This result demonstrates that PLP is a disruptive technology that is ideally suited for high yield, cost-effective production of medium-format IRFPA.

Beside its compliance with the currently targeted market, PLP turns out as a scalable technology to address a broad set of applications. Its pixel-wise architecture gives a natural and straightforward scalable capability as a function of pixel count (see Fig. 2). Moreover, the scalability of the technology was also demonstrated through the achievement of two different pixel designs which differ by their thermal insulation. In both cases, the product of NETD by the thermal time constant is unchanged and amounts to 550mK.ms. This major outcome, indicates that thermal insulation of a PLP pixel is essentially controlled by the leg's thermal conduction rather than the residual vacuum level. It is a key point to further address the reduction of the pixel pitch. A reduction of the leg width from 0.8µm down to 0.3µm is expected to suffice for the reduction of the PLP pixel pitch from 34µm to 17µm, respectively.

#### Related Publications:

<sup>[1]</sup> Yon J.J. et al, "Latest amorphous silicon microbolometer developments at LETI-LIR", Proc. SPIE Vol. 69401W, 2008.

<sup>[2]</sup> Fieque B. et al, "Uncooled amorphous silicon XGA IRFPA with 17µm pixel-pitch for high end applications", Proc. SPIE Vol 6940, 69401X,

<sup>[3]</sup> Yon J.J. et al, "320x240 uncooled IRFPA with pixel wise thin film vacuum packaging", Proc. SPIE Vol. 8541, 85410D, 2012.

## **Uncooled Terahertz bolometer arrays and camera**

#### Research topics: THz, micro-bolometer, imaging, spectroscopy, Mie scattering in

F. Simoens, F. Guellec\*, J.L Ouvrier-Buffet, S Martin, S Pocas, and J. Meilhan (\*LETI/ DACLE)

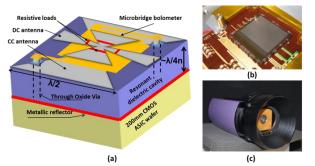

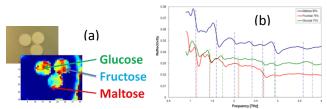

ABSTRACT: Thanks to its mature know-how in thermal infrared bolometer sensors, CEA-Leti has designed and fabricated proprietary uncooled QVGA terahertz bolometer arrays with unique antenna-coupled architecture. The characterization of the prototyped arrays integrated in a camera has demonstrated state-of-the art sensitivity in video camera operation mode. Real-time active imaging capabilities have been tested in several set-ups. In particular THz spectro-imaging has been demonstrated for discrimination of sugar powders compressed in pellets. The Mie scattering at terahertz frequencies in powder materials has been specifically studied in order to extract the spectral signatures necessary for spectro-imaging analysis.

For several decades, cooled bolometer imaging arrays have been developed for ambitious spatial programs and extremely sensitive bolometer FPA are being operated in low-background platforms or satellites for scientific researches. Some institutes are now trying to decline this know-how to larger volume applications, with some promising demonstrations like the video-rate THz camera developed by the VTT-NIST collaboration.

Nevertheless, even if uncooled bolometers are much less sensitive than cooled thermal sensors, they are in a position to meet easily large-scale commercial market. In particular, thanks to the maturity of the bolometer technology, THz-customized room temperature bolometers can potentially suit many applications that require 2D sensors with low cost in production (standard Si microelectronics) and operation (no cooling), compactness (monolithic), and 2D real-time & advanced image functions (array above CMOS). And indeed, uncooled microbolometer focal plane arrays (FPAs) are nowadays recognized as a relevant technology for fast 2D imaging compact, with commercial hand-held cameras by NEC or INO. The reader of this paper is invited to refer to the chapter written by Leti for a general review of bolometers for THz sensing ([1])

Thanks to its strong know-how in thermal infrared bolometer sensors, CEA-Leti has designed and fabricated proprietary QVGA terahertz bolometer arrays with unique antennacoupled architecture (Figure 1).

Figure 1: Uncooled THz antenna & cavity coupled microbolometer pixel structure (a). Prototyped 320x240 pixel array chip (b). Camera prototype integrating the THz bolometer array in its vacuum packaging (c). (extracted from reference [2])

The characterization of the prototyped arrays integrated in a camera (b & c of Fig 1) has demonstrated state-of-the art sensitivity in video camera operation mode : a minimum detected power par pixel of the order of 30 pW has been measured at 2.5THz.

Real-time active imaging capabilities of the prototyped 2D FPAs have been tested in several set-ups, both in reflection and transmission configurations. In particular THz spectro-imaging applied to the discrimination of sugar components has been demonstrated with fructose, glucose and lactose powders compressed in pellets imaged in reflection conditions (a in Fig 1). The spectro-imaging method combines multicolor THz images and a data base of the spectral reflectivity of these materials (refer to b of Figure 2).

Figure 2 : (a). visible and THz image of the sugar pellets (b). Spectral reflectivity of the sugar components characterized in collaboration with the University of Savoie (IMEP-LAHC)

The acquisition of this data base requires careful experimental preparation and data analysis. In particular the University of Savoie and CEA-LETI have studied the scattering effect in the powder materials with grain size of the order of the wavelength [3]. In such conditions, scattering effect cannot be well predicted by the simple models like the one by Raman or by the Christiansen approach: modelling using Mie theory is necessary in order to describe the absorption and scattering phenomena, and to evaluate its contribution to the THz power attenuation in the powders. For typical sub-millimeter size particles, the scattering contribution reaches 80~90% of the total power attenuation, even at frequency for which the particle material shows a rather strong absorption. The scattering contribution to the total losses greatly depends on the particles characteristics as size, distribution, shape, intrinsic refractive index and absorption. These models have been applied in order to extract the spectral fingerprints of sugar powders.

Related Publications:

[1] Simoens F., "Bolometric Detectors', chapter of Springer book 'Physics and Applications of Terahertz Radiation", Springer Series in Optical Sciences, Vol. 173, (2014)

[2] F.Simoens and J.Meilhan, "Terahertz real-time imaging uncooled array based on antenna- and cavity-coupled bolometers", Phil. Trans. R. Soc. A 28 March 2014 vol. 372 no. 2012 20130111; doi:10.1098/rsta.2013.0111, (2014)

[3] F. Garet, M. Hofman, J. Meilhan, F. Simoens and J.-L. Coutaz, "Evidence of Mie scattering at terahertz frequencies in powder materials", Appl. Phys. Lett. 105, 031106 (2014); http://dx.doi.org/10.1063/1.4890732

# Demonstration of large field of view fast scanning based on a realtime uncooled antenna & cavity coupled bolometer array camera

#### F. Simoens, J.L. Lalanne-Dera, S Martin, S Pocas, S Gidon, W Rabaud and J. Meilhan

ABSTRACT: Real-life applications of terahertz (THz) systems often require fast imaging of large field of view of opaque scenes. Such features have been demonstrated by the development of a complete reflection active THz imaging system that combines QCLs as sources and antenna & cavity coupled micro-bolometer as THz video camera. While better than 1 mm resolution images of 40x60mm<sup>2</sup> illuminated surfaces are acquired in real-time, a rotating planar mirror provides fast scanning of large areas, e.g. 20 x 30 cm2 in less than 10 seconds. This paper gives an overview of the developed system and video demonstrations.

Uncooled microbolometer focal plane arrays (FPAs) tailored specifically for THz sensing are nowadays recognized as a relevant technology for fast 2D image acquisition by compact and hand-held cameras [1]. The LETI/ DOPT has developed and fabricated innovative 320-240 bolometric arrays: bolometric pixels that are coupled to antennas and a resonant quarter-wavelength cavity are processed above CMOS wafers with fully standard Si microelectronics technology. Broadband sensing and better than 30 pW NEP have been demonstrated in video mode in the 2-4THz range [2].

In order to demonstrate the capability of this camera in closeto-real life application conditions, a complete system [3] has been developed to provide fast scanning of large field of view of opaque scenes. We reported spectro-analysis of single image acquired by this system [4]. This paper emphasizes the fast acquisition of large field resulting from the tiling of images.

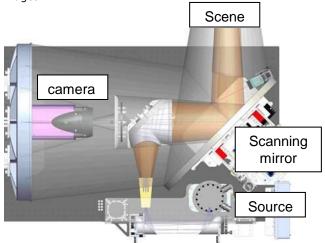

Figure 1: Large field of view fast scanning demonstrator scheme

The demonstrator combines a QCL THz source, an optical system and an uncooled bolometer camera, each of these components being optimized for operation in the vicinity of 2.5 THz (Fig. 1).

The scanning of the scene is ensured by a reflective mirror located on an alt-azimuth mount.

Thanks to a confocal scheme, this movement ensures simultaneously fast illumination and collection of the signal reflected by the scene. Then a 80 cm paraboloid mirror focuses the beam onto the camera FPA with an equivalent f/0.8 relative aperture.

Figure 2: Visible (the shirt has be removed for clarity) and THz image of a objects hidden under a shirt on a human trunk

The mirror is successively moved to cover the targeted large FoV. For each mirror position a switched source ON/OFF acquisition of the scene is operated by the camera that delivers the differentiated frame. The single image that is then acquired in real-time corresponds to 40x60 mm<sup>2</sup> illuminated surfaces.

The fast actuator and mechanical configuration of the system were optimized in order to dump vibrations during displacement of mirrors. The camera allows the scanning of a human trunk, typ. 20x30cm2, in 10 seconds.

High spatial resolution -i.e. less than 5mm- of hidden objects under a shirt has been achieved (Fig. 2).

This work has demonstrated that uncooled THz cameras can be applied to fast scanning of large areas in reflection configuration. Such features are suitable to many applications in different domains where opaque materials and objects are hidden by obscurant.

#### Related Publications:

[1]. F. Simoens, Physics and Applications of Terahertz Radiation', Chapter 2 'THz Bolometer Detectors', Springer Series in Optical Sciences,

vo. 173, pp. 35-75, 2014, ISBN 978-94-007-3836-2.

[2]. F. Simoens & J Meilhan, 'Terahertz real-time imaging uncooled array based on antenna- and cavity-coupled bolometers'. Philos Trans A

Math Phys Eng Sci.; pp.372, 2014

[3]. F. Simoens et al., "Complete THz system for reflection real-time imaging with uncooled antenna-coupled bolometer arrays," Infrared, Millimeter, and Terahertz Waves (IRMMW-THz), 2012 37th International Conference on, Dove Press, vol. 5, pp. 45-52, 2012.

[4]. J. Meilhan, et al., 'Reflection 2D real time THz camera to image and identify sugar pellets', IRMMW-THz Conf., 2013, doi : 10.1109/IRMMW-THz.2013.6665499

# Optical environmental sensors

Gas detection in Infra-Red

Non-dispersive IR sensors

Integrated photo-acoustic sensors

S. Nicoletti, P. Barritault, S. Boutami, M. Brun, A. Glière, P. Labeye, M. Carras\*, G. Maisons\* J. Czarny, H. Lhermet (\* III-V Lab)

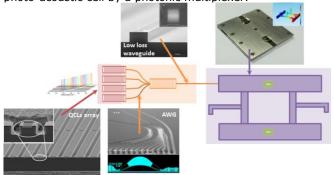

ABSTRACT: We present a compact optical gas sensor working in the MID-infrared by assembling a multi-wavelength QCL source with a small photo-acoustic cell (~ few cm3). The multi-wavelengths source is composed of QCL (Quantum Cascade Laser) array coupled to photonic combiner. QCL array have been fabricated through an original approach that greatly simplifies the fabrication anf improves the yield. The wavelength of each laser can also be selected independently after the growth of the epitaxial layers. Low loss waveguides based on SiGe alloy have been achieved with losses <1dB/cm at 4.5 μm, <1.5 dB/cm at 5.65 μm and <2dB/cm 7.4 μm. Mini acoustic Helmholtz cavities enabling a differential measurement have been designed and made by micro machining.

The photo-acoustic detection is based on the generation of an acoustic wave induced by the absorption of a laser pulse. This absorption is due to the excitation of rovibrational energy levels of molecules in the mid-infrared. The absorbed energy is restored in the form of a transient heating, which generates a pulse wave measured by a microphone. The amplitude of the wave is directly related to the concentration of the compound in the ambient gas.

The QCLs sources were quickly considered well suitable for this kind of analysis technique. Indeed QCL wavelength range between  $3\mu m$  and  $11\mu m$  corresponds to most gases of interest (alkane, Volatile Organic Compounds, sulfur oxides and nitrogen oxides)[1]. Moreover, the power exceeds several mW, improving hence the limit of detection (LOD). QCLs coupled to photonics circuits, specifically engineered to guide the light over the spectral range, enable to achieve multi-wavelengths source for an efficient spectroscopic analysis of gas mixtures. Since each molecule has a distinct absorption spectrum which represents a unique "signature", the choice of a given adsorption peak or of a characteristic band of the spectrum allows to detect the chemicals and to estimate their concentration. The paper presents some major achievements toward the miniaturization of such an optical sensor fabricated by merging on the same chip different functionalities spanning from integrated optics, fluidics, acoustics and electromechanical transduction.

A schematic of the devices is shown in figure 1: the output of each source in the QCL array is combined into a miniaturized photo-acoustic cell by a photonic multiplexer.

Figure.1: Schematic of the fully integrated sensor including an array of QCL sources, a multiplex to combine and drive the laser outputs and the MEMS photo-acoustic cell.

The widely tunable Mid-IR QCLs, Fig.1, have recently been developed [2] through a proprietary metal grating approach

- 1 S. Nicoletti et. al., IEEE Sensors 2014. Proceed-ings (2014), p. 649. 2 G. Maison et al., 2014International Semiconduc-tor Laser Conference (ISLC) Proceedings (2014), p. 169

- 3 M. Brun, et. Al., OPTICS EXPRESS Vol. 22, No. 1 (2014), p. 508

- 4 A. Glière, et al., Int. J. Thermophys (2013), 34, p. 2119 & A. Glière, et al., SENSORS (2014), Vol. 14 p. 957

where the feedback in the cavity comes from the interplay between guided waves in the active medium and surface waves at the interface with the metal grating. The wavelength of each laser can be selected independently after the growth of the epitaxial layers. Moreover, a strong coupling can be obtained without the use of buried grating and the second mode is suppressed because of the higher losses while principal mode is favored.

Photonic multiplexers (at 4.5µm and 7.4µm) (see Fig. 1.) based on specific SiGe technology (having step index profile and graded index profile in the in-plane and out-plane direction, respectively) were fabricated and characterized. Losses of such waveguides were <1dB/cm at  $4.5 \mu m$ , <1.5 dB/cm at 5.65 μm and <2dB/cm 7.4 μm, which represent to our knowledge, state-of-the-art performances for this wavelengths range [3].

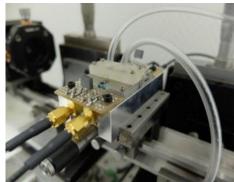

Figure.2: Set-up for gas measurement with photo-acoustic cell

The small differential Helmholtz resonator (DHR) [4] has been investigated. In DHR two identical chambers are connected by two capillaries. Although only one chamber of the sensor is illuminated by a laser beam, acoustic waves are established in both chambers allowing an intrinsic differential measurement. This scheme is also relatively insensitive to the shape of the energy deposition localization [4] and keeps constant pressure in each chamber.

The feasibility of such a system based on the assembly of QCLs, a multiplexer and a photo-acoustic cavity has recently been demonstrated. A Limit Of Detection of 1ppm has been reached injecting diluted CH4 gas in a carrier gas, Fig. 2.

# Towards non linear conversion from mid to near infrared wavelengths using silicon germanium waveguides

#### Research topics: gaz sensors, mid infrared, non linear optics

P. Labeye, E. Lorent, D. Jacolin, S. Ortiz, J.-M. Hartmann, S. Nicoletti, B. Adonis, A. Kapsalis, K. Hammani, M. Ettatib, P. Petropoulos, D. Syvridis.

ABSTRACT: We report on nonlinear conversion from mid infrared to near infrared optical wavelengths in silicon germanium waveguides using phase-matched four wave mixing. These waveguides, originally developed for gas sensing by infrared spectroscopic optical absorption, offer interesting non-linear characteristics and could lead to new detection schemes for gas sensing.

The mid-infrared (mid-IR) spectral region has attracted a significant amount of interest during the past few years. It contains the absorption "finger-prints" of most molecules of interest, thus suggesting several applications both in spectroscopy and chemical and biomolecular sensing. The recent development of mid-IR sources, most notably quantum cascade lasers (QCLs)[Y. Yao, (2012)], has further stimulated the interest of the research community in this area. However, the lack of small size, room temperature detectors exhibiting suitably high sensitivity at this wavelength region still remains an issue.

To overcome this issue, wavelength conversion of the midinfrared signals to the near-infrared is a promising alternative. This conversion can be performed either through sum-frequency generation in a second-order nonlinear medium, such as periodically poled lithium Niobate [K. D. Buchter (2009)], or through four-wave mixing (FWM) using a third-order nonlinear medium, such as silicon [B. Kuyken (2011)]. Silicon is an excellent candidate for such applications, thanks to its transparency up to 7µm, reduced two-photon and free-carrier absorptions beyond 2µm and its potential for monolithic integrated solutions. These features however, are not restricted to pure silicon. For instance, silicon germanium (SiGe) alloys have been identified as promising candidates for nonlinear applications in the mid infrared and long infrared thanks to their enhanced nonlinearity compared to pure Si [N. K. Hon (2011)].

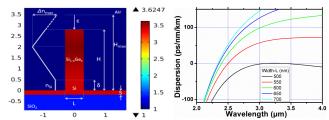

In this context, and using our SiGe grade index waveguide platform [1], we adapted the waveguide geometry in order to obtain good nonlinear characteristics, namely: a) Strong confinement with small effective mode area for intense nonlinearities, b) low loss throughout the wavelength span c) sufficient coupling with the dominant mid-IR sources, e.g. QCLs, and d) zero dispersion around 2  $\mu$ m.

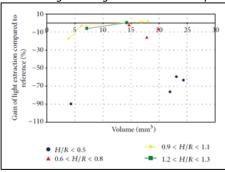

The waveguide design as well as simulated dispersion curves is shown in Fig.1. The main factor affecting the waveguide dispersion is the ratio H/L. For a given H value, an increase in L results in a blue shift of the zero dispersion wavelength. However by further increasing the waveguide width, the effective mode area becomes too large to support strong nonlinear phenomena.

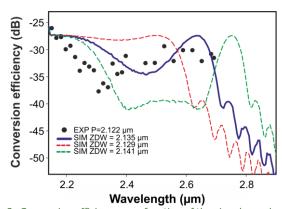

Fig. 2 summarizes the measurements and compares them with numerical simulations which considered an input launched power of 75 mW for the pump, 10 mW for the signal, and waveguide losses of 2 dB/cm, in line with the

experimental values. The comparison is in qualitative agreement.

Figure 1: LEFT: schematic view of the waveguide structure. RIGHT: theoretical dispersion curve for 5 different widths (H=2.05 $\mu$ m,  $\delta$ =1 $\mu$ m).

Figure 2: Conversion efficiency as a function of the signal wavelength. Comparison between experiments (black dots) and numerical simulation for the dispersion shown in Fig. 1 (blue solid line) and for the zero dispersion shifted of + 6 nm (green dashed line) and - 6 nm (red dashed line).

The figure 2, also demonstrates a Conversion Efficiency of -32 dB for the conversion from 2650 nm to 1771 nm, which represents one of the highest values ever reported. Note that it was not possible to demonstrate broader conversion than this due to limitations in the tunability of the lasers used. This work was supported by the European Community Seventh Framework Program FP7/2007-2013 under Grant 288304 (STREP CLARITY).

[1] M. Brun & al, "Low Loss SiGe graded index waveguides for mid-IR applications", Op. Ex. 22 (1) pp508-518 (2014)

# Optimization of a radiative membrane for gas sensing applications based on NDIR method

#### Research topics: gas sensing, MEMS, membrane, spectral efficiency

Anthony Lefebvre, Salim Boutami, Jean-Jacques Greffet\*, Henri Benisty\*

(\* institut d'Optique, CNRS, France)

ABSTRACT: In order to design cheap and efficient sources of radiation for gas sensing applications, we propose a model to optimize the device wall-plug efficiency relative to application driven constraints. Typically, suspended micro-hotplates realized using MEMs technology are used, but their efficiency is rather low. Considering constraints such as the available energy-permeasurement and the maximum operating temperature, we demonstrate that the size and the switch-on time of the membrane can be optimized in order to emit the largest possible amount of light in the gas spectral window of absorption. We also show that the efficiency can be drastically improved by tuning the hotplate emissivity to match this absorption profile, and provide an insight into the thermo-optical mechanisms governing these devices.

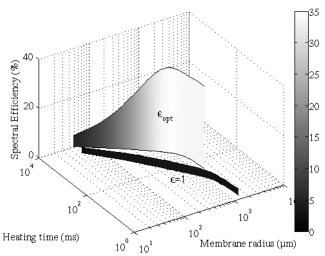

To engineer a cheap, portable and low-power optical gas sensors, incandescent sources are strongly competing expensive quantum cascade lasers and low-efficiency lightemitting diodes. Such sources of radiation have already been realized by us, using standard MEMS technology, consisting in free standing circular micro-hotplates. Once sealed under vacuum, the main drawback of these membranes is known to be the power lost through conduction to the substrate, thus not converted in (useful) radiated power. If the membrane temperature is capped by technological requirements, radiative flux can be favored by increasing the membrane radius. However, given a finite amount of energy (ensuring the low-power characteristic of the device), the larger the membrane and its heat capacity, the shorter the time it can be turned on. This clearly suggests that an efficiency optimum has to be found. We use a 1D thermo-optical model, based on hypotheses allowing us to retain the essential characteristics of the membrane depicted on figure 1, while drastically reducing the computation time compared to standard FDTD.

×400 ×25 0 m

Figure 1: SEM image of the modeled suspended membrane. Light grey areas are the electric tracks providing Joule heating.

These simulations are based on a spatio-temporal radial profile, which allow us to compute precisely the amount of

light emitted in the absorption window of the gas of interest, namely CO2 in this example. Only certain couples (membrane radius / heating time) are allowed in order to meet both the energy and the maximum temperature requirements, and an optimum is found as intuited, as depicted on figure 2.

In the case of a blackbody emission with unitary emission, efficiency is capped to a few percent, for even if conduction has been strongly reduced, most of the radiation is emitted outside the CO2 absorption window. In order to tackle this problem, we study the possibility of tuning the membrane emissivity, using optical coatings for example, in order to match closely the absorption window. In the optimum case where light is only emitted in this spectral range, the efficiency jumps by an order of magnitude, and is only limited by the conduction through the arms, see figure 2.

Figure 2: R(t) solution and corresponding spectral efficiency of the constrained thermal equations with E=5mJ and Tf=923K for the optimal emissivity and the unitary emissivity.

This optimization process can be made with different membranes, constraints, gases, and will always yield the best possible design in order to fabricate low-power, high efficiency thermal sources for gas sensing applications

Related Publications:

Lefebvre, A., Boutami, S., Greffet, J. J., & Benisty, H. (2014, May). Optimization of a radiative membrane for gas sensing applications. In SPIE Photonics Europe (pp. 91410G-91410G). International Society for Optics and Photonics.

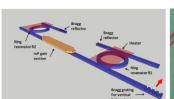

CMOS photonic III-V/Si devices

Modulators and receivers

Hybrid optical lasers

Photonic systems

# Low-crosstalk fabrication-insensitive echelle grating demultiplexers on Silicon-On-Insulator (SOI)

C. Sciancalepore, R. J. Lycett\*, J.-A. Dallery\*\*, S. Pauliac, K. Hassan, J. Harduin, H. Duprez, U. Weidenmueller\*\*, D. F. G. Gallagher\*, S. Menezo, and B. Ben Bakir (\*Photon Design Ltd., Oxford,UK, \*\* Vistec Electron Beam GmbH, Jena, D)

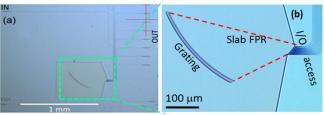

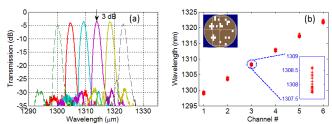

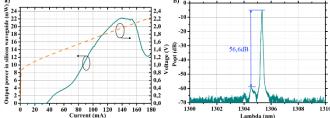

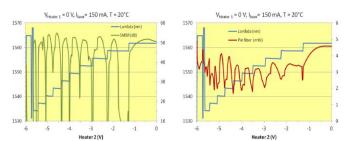

ABSTRACT: In this communication, we report about the design, fabrication, and testing of echelle grating (de-)multiplexers for the 100GBASE-LR4 norm in the O-band (1.310 nm) for Silicon-based photonic integrated circuits (Si-PICs). In detail, 20th-order echelle gratings on the 300-nm-thick SOI platform are designed for 4x800-GHz-spaced wavelength division multiplexing. The devices are featuring extremely low crosstalk ( $\sim$  -30 dB), precise channel spacing, and optimized insertion losses (-3 dB). State-of-the-art absolute lambda registration over the wafer and the lot claim the excellent robustness of these demonstrators.

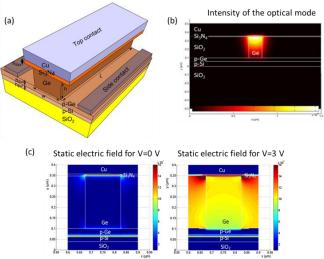

Silicon-on-insulator (SOI) high-index contrast allows for the small-footprint implementation of optical functions constituting the whole silicon photonics toolbox such as optical resonators, laser sources, input/output (I/O) couplers, high-speed modulators, Si-Ge photodiodes, as well as filters and wavelength (de)multiplexers.

Concerning the latter, wavelength-division multiplexing (WDM) constitutes an essential building block for the development of high-capacity inter-rack, inter-board optical interconnects and on-chip transceivers. Optical filters working as wavelength (de-)multiplexers (WMUX) are needed for reaching higher aggregate system bandwidths, by transmitting/receiving data over several optical carriers. Specifically, a low crosstalk at the receiver is crucial for ensuring a correct data transfer at high rates, while a precise interchannel spacing and a minimized non-uniformity are necessary to minimize insertion losses. Moreover, wafer- and lot-level performance stability is essential for power-efficient transceivers, as the active realignment of the spectral comb transmission peak respect to absolute ITU grid wavelengths represents an extra thermal and power budget.

Figure 1: Optical images (a, b) of the echelle grating (de)multiplexers.

In diffractive-based echelle gratings (EGs), phase delay is obtained by using a free propagation region (FPR) comprising a slab waveguide, while the chromatic dispersion is attained via the wavelength-dependent reflection from a high-order (usually m>10) diffraction grating.

Echelle gratings are diffraction grating spectrometers whose principle is based upon phase matching the light reflected from neighboring facets. In addition to the diffractive properties, the shape and the curvature of an echelle grating provides, at a given wavelength, the focusing of the input waveguide mode onto the plane of the output waveguides.

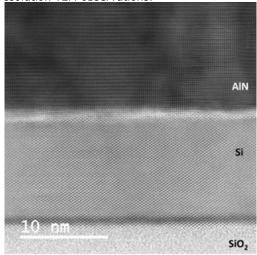

Optical and scanning electron microscope (SEM) images of the echelle grating (de-)multiplexer are illustrated, respectively, in Figs. 1. The fabrication process made use of 200-mm CMOS pilot lines processing tools on SOI substrates, characterized by 310 nm of silicon over 800-nm buried oxide (BOX). Dose-optimized VISTEC variable-shape electronbeam (e-beam) lithography and HBr-based reactive-ion etching are used for the silicon patterning. High-density plasma (HDP) silica deposition is used for Si encapsulation, then followed by chemical-mechanical polishing (CMP) for surface planarization.

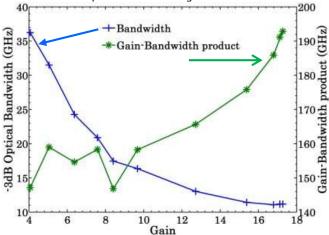

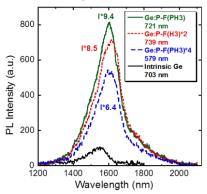

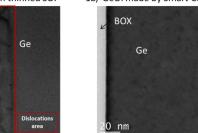

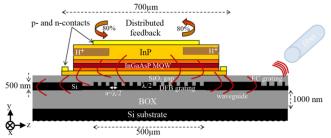

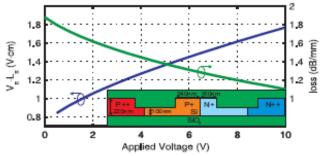

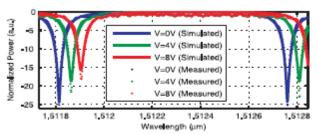

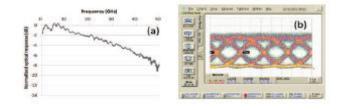

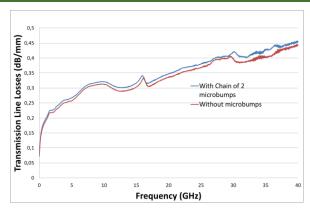

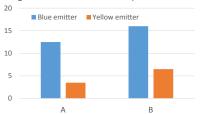

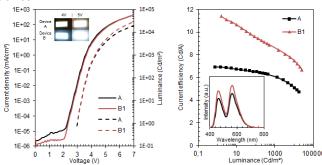

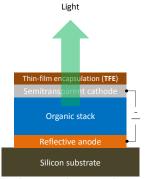

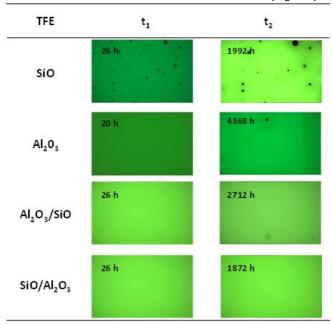

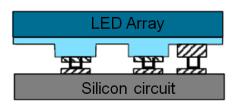

Figure 2: (a) 20th-order 800-GHz-spaced echelle grating transmission spectrum around 1310 nm. (b) Wafer-level channel-by-channel wavelength dispersion. Randomly-chosen dies (25) over the SOI wafer (upper left inset).