Cinq avantages fondamentaux du spin dans le silicium

Publié le 8 février 2024

Corps de texte 2

Bien que très prometteuse, l'approche s'appuyant sur du silicium, qui tire parti de technologies CMOS bien établies, est encore aujourd'hui confrontée à de grands défis en termes de développement. Elle offre toutefois un certain nombre d'avantages fondamentaux qui rendent son étude particulièrement attrayante. Parmi ces avantages, les plus importants sont les suivants :

Fonctionnement des dispositifs sur une plage de températures d'env. 1 K, plutôt que sur une plage de l'ordre du mK (proche du zéro absolu) dont l'approche "supraconducteurs" a, elle, besoin. Si cette différence peut sembler minime, la difficulté à atteindre et maintenir des températures plus faibles augmente de façon exponentielle à mesure que ces dernières approchent du zéro absolu. Cette marge supplémentaire en termes de budget thermique permet de faire fonctionner des systèmes d'importante envergure intégrant plus d'électroniques de contrôle classiques.

Résistance renforcée à la décohérence, grâce aux caractéristiques du silicium. Le phénomène de décohérence[1] est un défi fondamental pour l'informatique quantique, l'une des sources majeures de qubits de spin au sein de semi-conducteurs étant l'interaction entre les moments magnétiques des électrons et les spins nucléaires. Tandis que les matériaux semi-conducteurs III-V, tel qu'utilisés dans certains des travaux de développement quantique orientés photonique, incluent des spins nucléaires totaux non nuls, l'isotope majoritaire du Si, 28Si (qui représente 95 % du Si naturel), n'a pas de spin nucléaire net. De plus, le Si naturel peut être isotopiquement purifié à l'aide de la centrifugation, et ce quasi intégralement (état de l'art supérieur à 99,99 %). Résultat : un environnement magnétique remarquablement propre pour les qubits et donc une durée de vie plus longue pour les spins des électrons.

Vitesse de fonctionnement. Grâce à une structure dotée de plusieurs portes permettant un couplage direct, la plage de vitesse est de quelques µs pour tous les types de fonctionnement. Cela permet de garantir des délais de calcul raisonnables, de l'ordre de milliards d'opérations par heure, ce qui correspond bien à l'état de l'art actuel dans le domaine du traitement quantique.

|

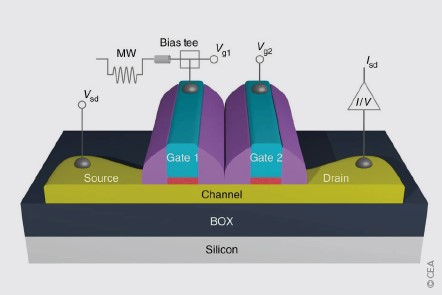

PREMIER DISPOSITIF QUBIT AU MONDE FABRIQUÉ SELON UN PROCESSUS STANDARD CMOS Schéma simplifié en 3D d'un transistor à effet de champ à nanofils en silicium sur isolant avec deux grilles. |

Possibilité d'isoler des électrons individuels au sein d'une structure fabriquée à l'aide de la technologie CMOS. Le contrôle des qubits est ainsi optimisé. Dans une récente interview, Maud Vinet, responsable du programme quantique au CEA-Leti, explique que la structure est, par nature, « un transistor doté d'une grande résistance d'accès. [Dans cette configuration], il sera très facile de [créer] un puits de potentiel entre deux résistances, une boîte quantique. Au sein de ce puits de potentiel, vous pouvez ensuite piéger un électron et manipuler son spin à l'aide d'un champ magnétique. Et voilà comment sont nés les qubits de spin dans le silicium ». Pour fabriquer des boîtes quantiques, le CEA-Leti s'est appuyé sur sa plateforme FDSOI en raison des multiples avantages qu'elle offre. Elle permet ainsi la mise en application des travaux cryo-CMOS FDSOI du CEA-Leti, à savoir des technologies CMOS pouvant fonctionner à des températures cryogéniques. En phase de développement, elle offre également la possibilité d'utiliser une grille arrière (back-gate) permettant aux dispositifs de contrôler in situ les puits de potentiel qui confinent les qubits. Pour la fabrication d'un processeur quantique full-stack intégrant des composants électroniques de contrôle résistants à de faibles températures, la technologie FDSOI semble en outre être le meilleur choix, l'utilisation de plateformes technologiques identiques pour les qubits et les composants électroniques de contrôle simplifiant la co-intégration.

- Densité d'intégration élevée, qui facilite l'évolutivité vers de plus grandes matrices de qubits. L'industrie des semi-conducteurs a un atout unique, celui de fabriquer facilement et économiquement des milliards de microstructures identiques, à l'instar des transistors. Des travaux préliminaires réalisés par le groupe Quantum Silicon Grenoble ont démontré la possibilité de fabriquer des structures multicouches pour positionner des boîtes quantiques CMOS à proximité immédiate de transistors à un électron (SET) en les espaçant de 100 nm. Cela permettrait de créer jusqu'à 106 qubits sur une surface de 100 microns² (0,1 mm), avec la possibilité d'un fonctionnement en parallèle, des considérations importantes pour une architecture d'informatique quantique à grande échelle.

[1] voir ANNEXE, Héritage du CEA dans la recherche quantique et approche silicium

Haut de page